mirror moduse v False lif operation => (LRROP mirror moduse v. false mirror moduse v. false mirror moduse v. frue mirror moduse v. false lif operation v> (MIRROP 2": mirror moduse v. false mirror moduse v. false mirror moduse v. false mirror moduse v. false mirror moduse v. false

#selection:atotheshul &

mirror\_ob.selected modius

modifier\_ob.select=1

bpy.context.scene.objects.at

# **SILVACO**

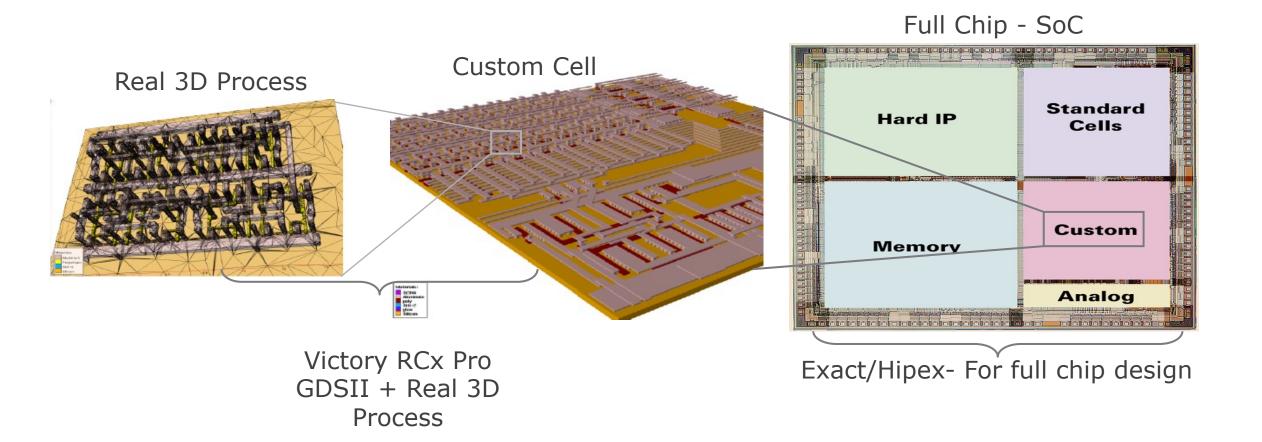

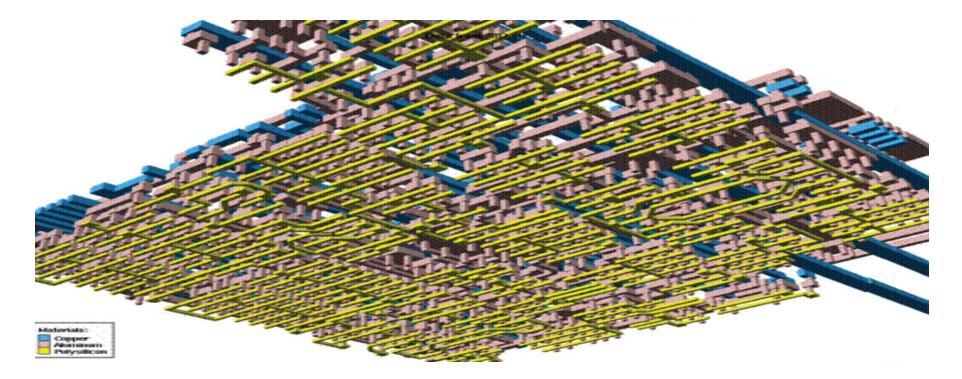

# Victory RCx Pro RC – Extractor for 3D Structures

Technology-Driven Parasitic Extraction Tool

# Applications

- Victory RCx fits well as an RC extraction tool in the following markets:

- Deep submicron CMOS

- Realistic 3D back end process simulations and accurate interconnect simulation with user selected tolerance

- Accurate via detailed capacitance and process analysis of individual problematic features, such as 45 nm via structures

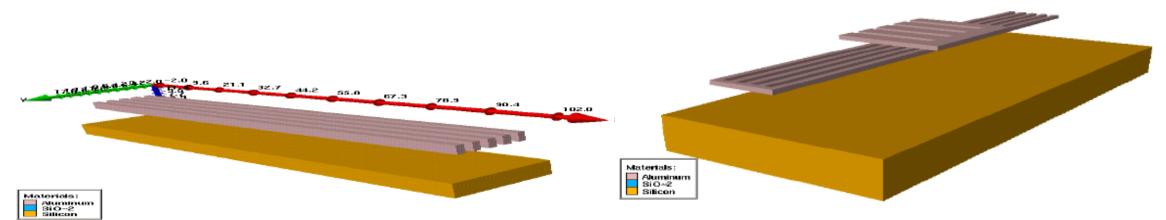

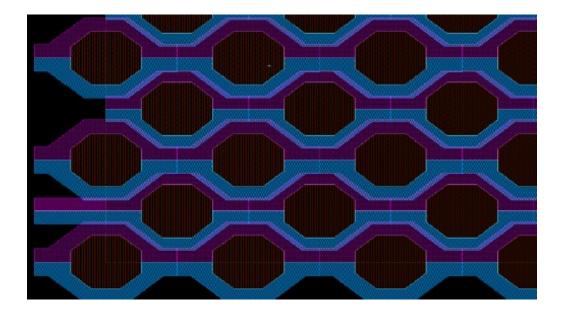

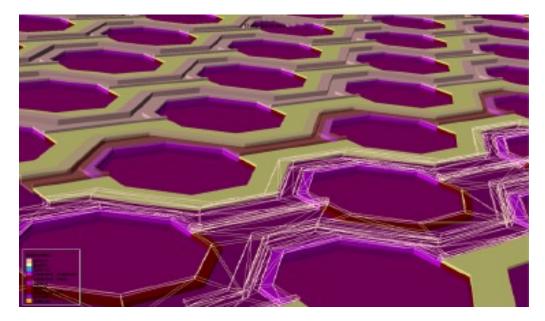

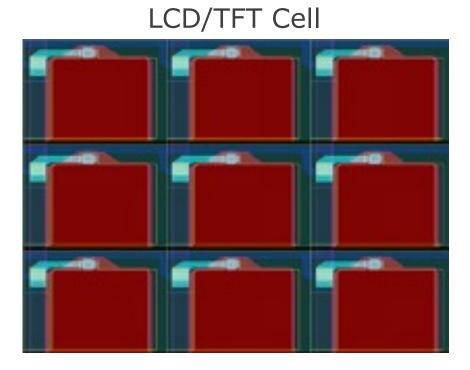

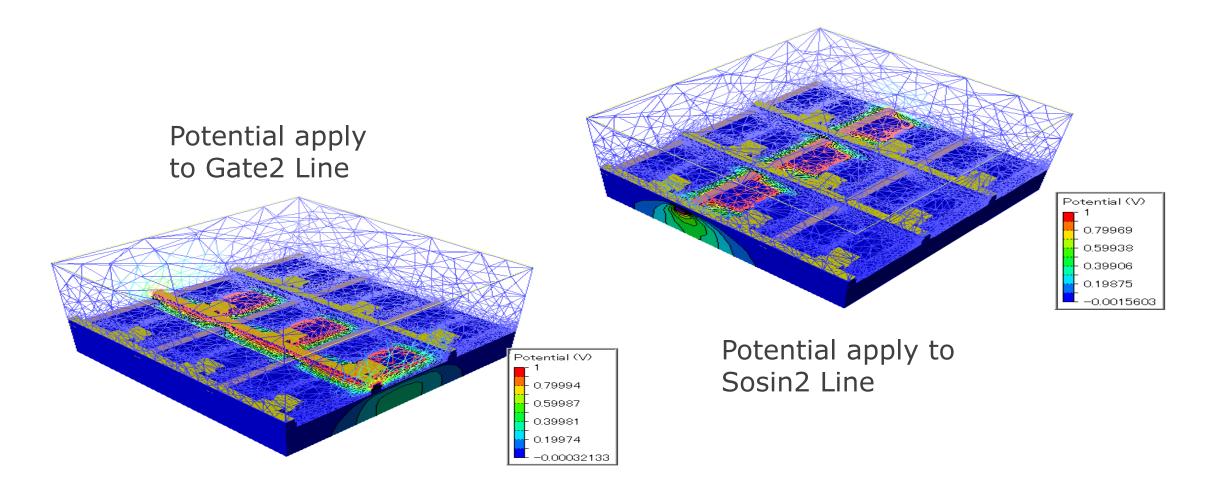

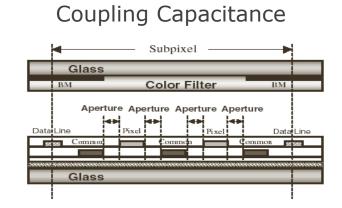

- Flat Panel LCD and TFT circuits

- Special features to deal with high aspect ratio structure

- SED Television technology

- Memory manufacturing

- SRAM and Flash Memory cell

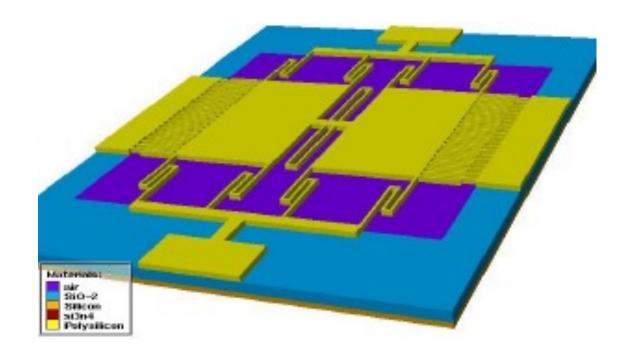

- MEMS simulation

- Systems-on-a-chip brings together silicon-based microelectronics with micromachining technology

#### **Benefits**

- Advanced lithography and realistic etch deposition models are used to create realistic structure

- Conductor and Insulator Field Solvers based for high accuracy capacitances and resistances calculation

- Accurately solves critical 3D back end process steps (e.g. dual damascene, thin layer deposition)

- Increase productivity with fast, multi-threaded 3D process simulation

- Optimize circuit performance as a function of back end process parameters and layout parameters

- Solve process integration issues due to layout design errors

- High level of automation (integrated in the VWF)

#### Advantages

- No restriction on geometry size 65nm, 45nm and below

- Realistic Structure Generation suitable for all technologies and arbitrary 3D shapes

- Only RC extractor in the industry capable of reproducing the lithographic effects of Optical Proximity Correction (OPC) sub wavelength effects, phase-shifts mask (PSM), misalignment, defocus, and ∆CD

- True 3D, mask driven process simulation

- Realistic deposition, etch and photolithography

- Netlist extractor to extract active device SPICE netlist

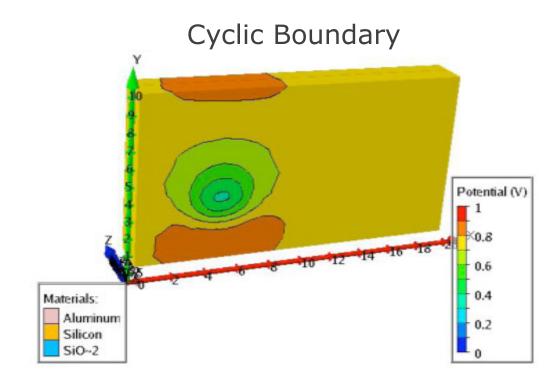

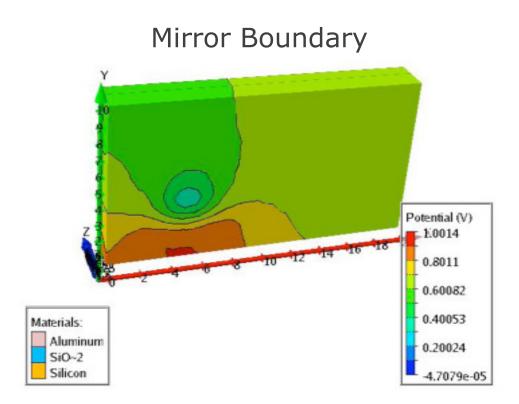

- User selectable boundary condition

- User definable materials names and properties

# Advantages (con't)

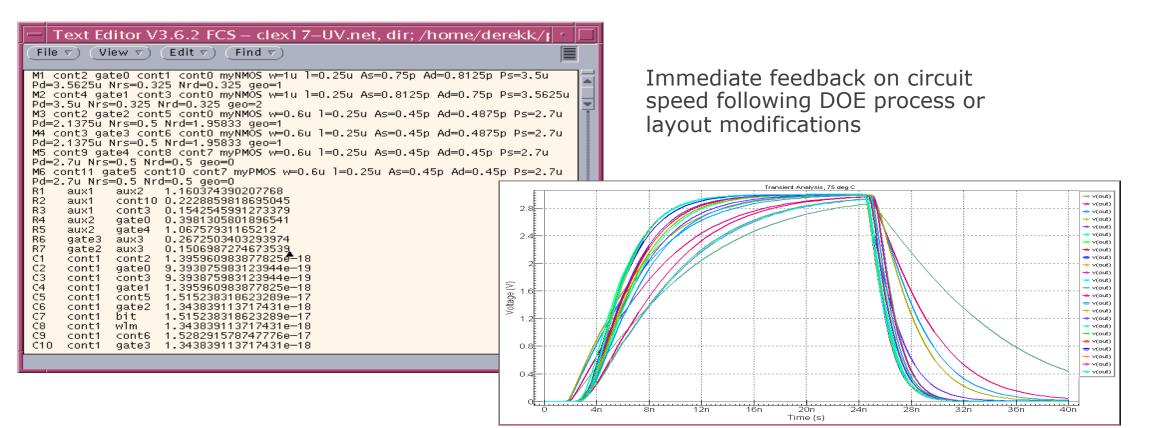

- Automatic back annotation of field solved resistances and capacitances onto extracted active device netlist for immediate SPICE analysis

- Full 3D field solver engine directly calculates parasitic RC extraction for best accuracy and handle dummies

- Automatic grid generation and refinement during 3D field solver calculation of capacitance and resistance

- Versatile small cells using fully realistic 3D processing or larger cells using geometric processing

- User-defined tolerance control on extraction accuracy

- 2D/3D structure Viewer (TonyPlot2D/3D)

- Post-processing tools to make capacitance and resistance models and optimization

- Symmetric boundary condition to allow users to perform Cyclic Simulations

- Selective area parasitic extraction enables maximum accuracy for critical layout windows

#### Victory RCx Pro – Simulator

## Victory RCx Pro – Simulator

- Simple intuitive Mask Driven process

simulation syntax

- Easy to learn and use

- User friendly input file development and runtime environment

| 📃 — Deckbuild V3.28.0.R – clex17.in, dir; /home/derekk/presentatic 🕤 🗌                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $(File \ \overline{\nabla}) \ (View \ \overline{\nabla}) \ (Edit \ \overline{\nabla}) \ (Find \ \overline{\nabla}) \ (Main \ Control \ \overline{\nabla}) \ (Commands \ \overline{\nabla}) \ (Tools \ \overline{\nabla})$ |

|                                                                                                                                                                                                                           |

| go victoryrcx                                                                                                                                                                                                             |

| Init Layout—"clex17.lay" Depth—1.0 Silicon Map—"clex17.lmp"                                                                                                                                                               |

| Save Layout—"clex17_1.lay" Spice—"clex17_1.net"                                                                                                                                                                           |

| Electrode Substrate                                                                                                                                                                                                       |

| ## Process Description ##                                                                                                                                                                                                 |

| Illumination Wavelength-DUVLINE                                                                                                                                                                                           |

| Deposit Resist Thickness=0.1 Max                                                                                                                                                                                          |

| Mask "AA" Litho CriticalIntensity-0.5 Aperture-0.5 Defocus-0                                                                                                                                                              |

| Etch Silicon Rate-1 Time-0.5 Isotropic-0.1                                                                                                                                                                                |

| Strip Resist                                                                                                                                                                                                              |

| Deposit Oxide Thickness=0.005                                                                                                                                                                                             |

| Mask "*GATE" reverse                                                                                                                                                                                                      |

| (next) (line) (stop ⊽) (cont) (run) (quit) Line: 1                                                                                                                                                                        |

|                                                                                                                                                                                                                           |

| CLEVER                                                                                                                                                                                                                    |

| Version 3.8.6.R                                                                                                                                                                                                           |

| CLEVER started CLEVER                                                                                                                                                                                                     |

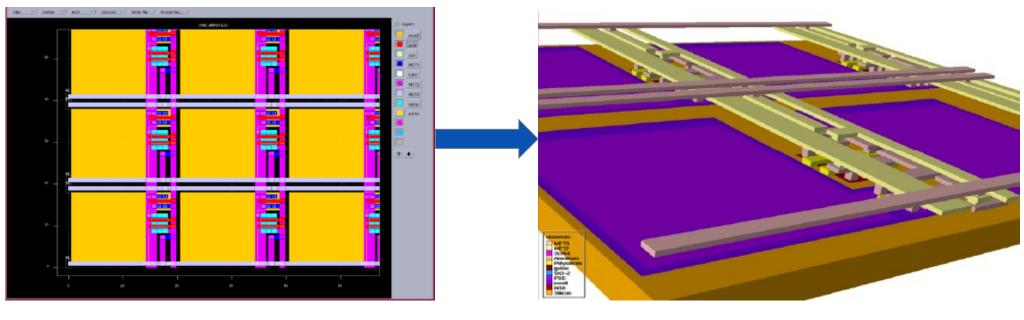

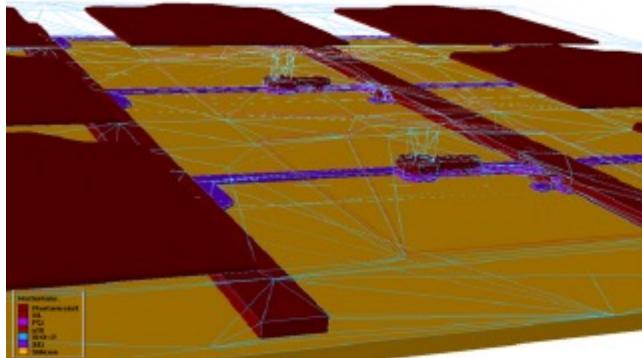

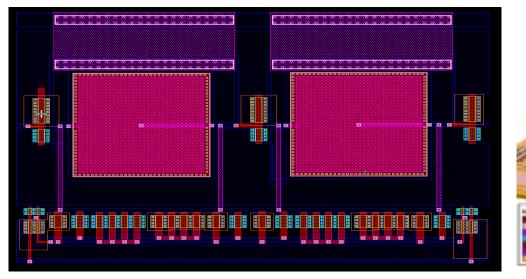

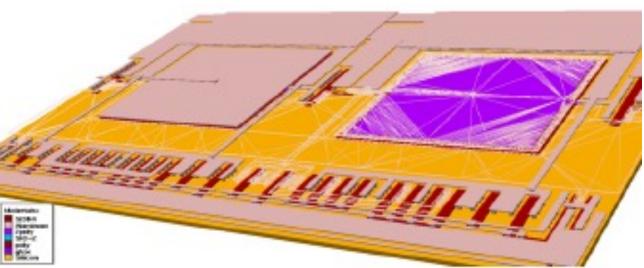

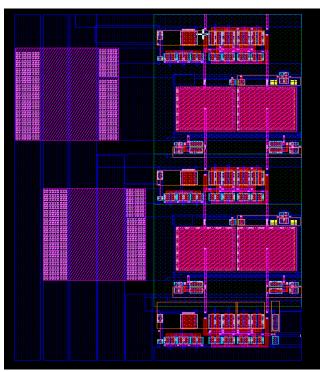

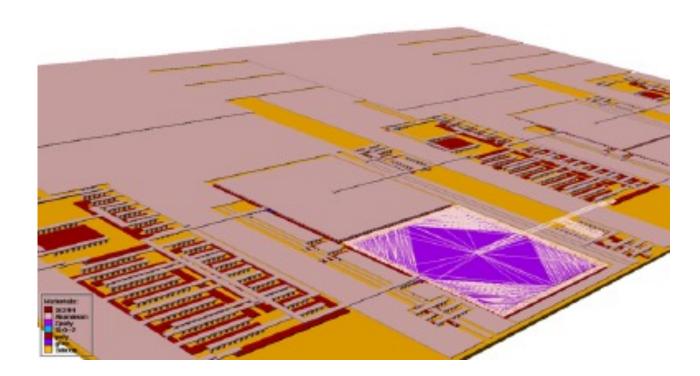

#### Victory RCx Pro – Layout Driven

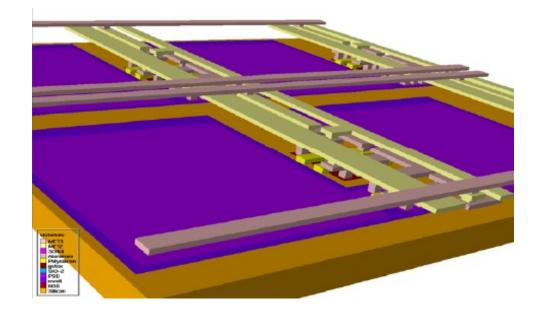

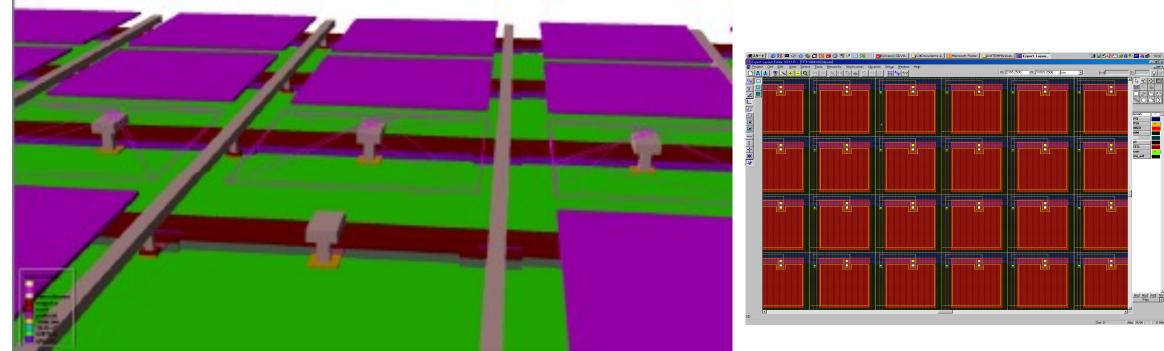

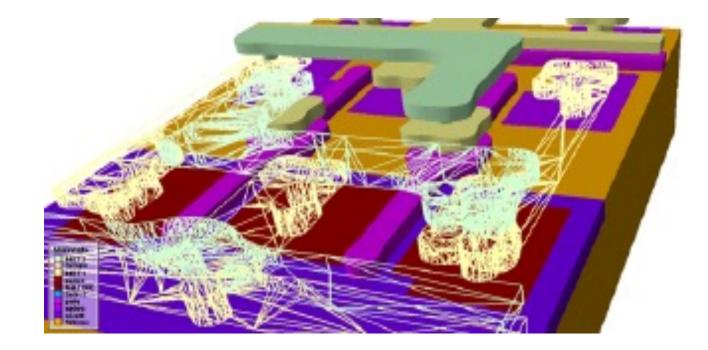

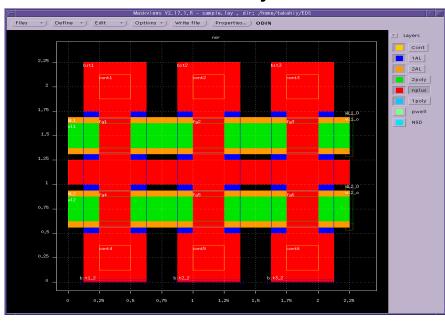

• 3D structures created from Mask Driven intuitive process commands

GDS2 Mask Layout

3D Structure

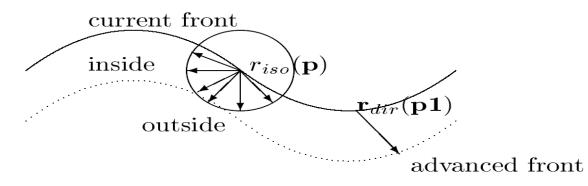

Victory RCx Pro simulates realistic geometric etch and deposition steps very efficiently with unstructured tetrahedral mesh - the developed algorithm combines the efficiency of string methods and the robustness of Level Set methods

#### A generic model for etch and deposit

Illustration for one step of the moving front;  $r_{iso}(p)$  is isotropic etch rate at point p, and  $r_{dir}(p1)$  is directional etch rate at point p1.

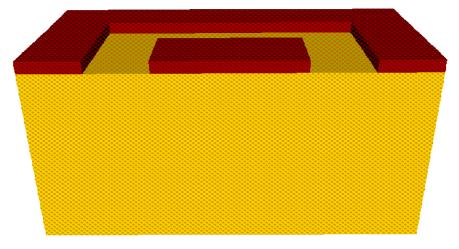

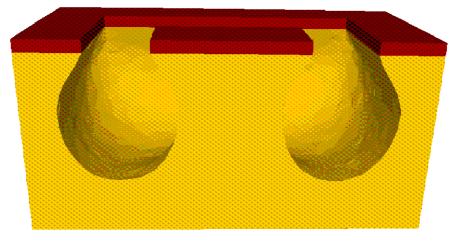

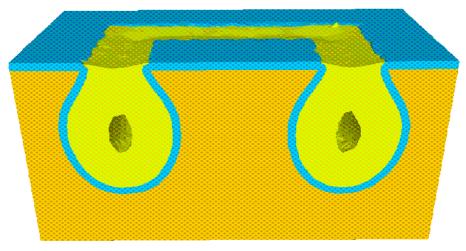

• Example – creation and refill of a trench structure

Patterning of photoresist.

Directional etching;  $r_{dir}$  is determined by the visible "cone" from above.

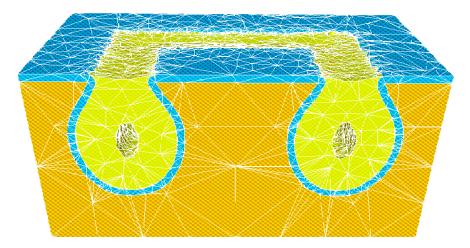

• Example – creation and refill of a trench structure

Trench refill; illustration of void creation.

Final trench structure with mesh.

- Complex etching capability

- Difficult Etch/Deposit Combinations Possible

Optional geometric deposition/etch allows much larger circuits to be simulated using the same memory

#### Victory RCx Pro – Back Annotation

Automated annotated SPICE netlist generation

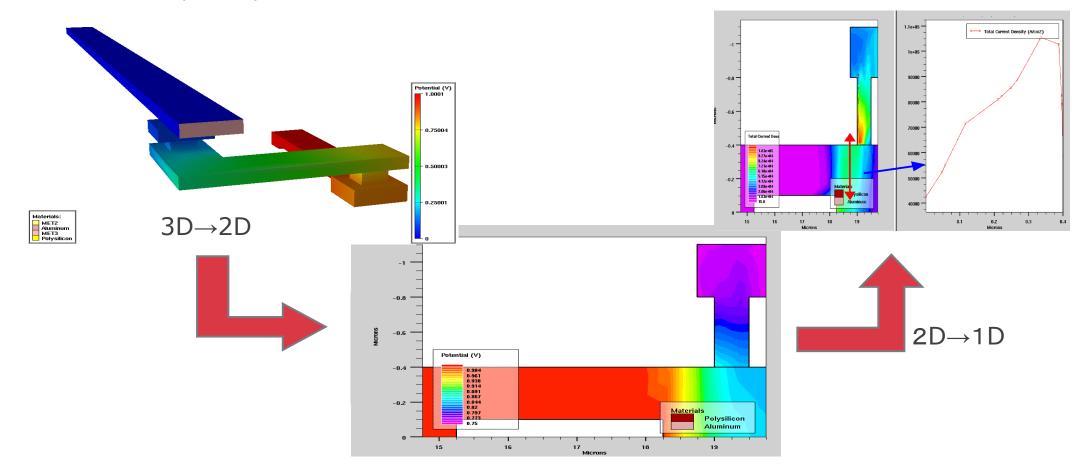

#### Victory RCx Pro – Current Density

• Current density analysis

#### **Case Studies**

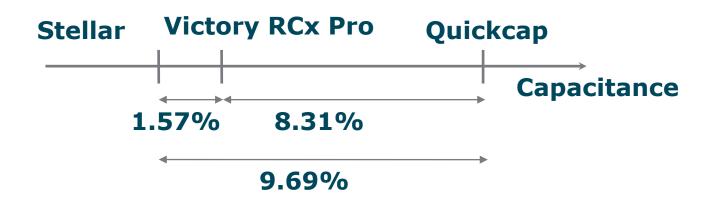

- Capacitance extraction on 83 layouts with, Victory RCx Pro, QuickCap and Stellar

- Deep submicron CMOS

- Flat panel

- Memory Cells

- MEMS simulation

- Local Interconnect

- Capacitance extraction with QuickCap, Victory RCx Pro and Stellar

- Layouts

- Among the 83 layouts, we find 3 families :

- Long parallel lines (73)

- Combs (8)

- Special process (2) (non-planar)

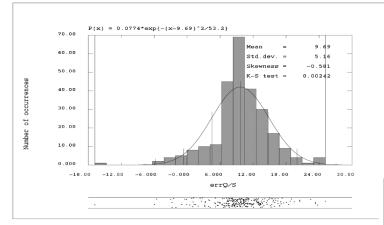

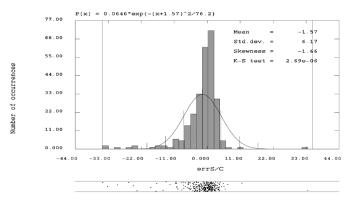

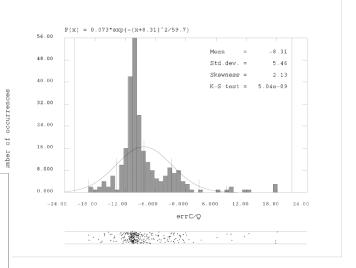

• The error is calculated as:

$$errX/Y = \frac{X-Y}{(X+Y)/2} \times 100$$

- The total number of capacitances extracted is 270

- Analysis

- The analysis is made using Spayn

- The data set of errors has been filtered (3 sigma filtering) and 261 values have been retained (96.67% of the total)

- Errors are displayed in histogram fitted with a gaussian distribution

#### Quickcap vs Stellar

Stellar vs Victory RCx Pro

#### Quickcap vs Victory RCx Pro

#### SILVACO

Copyright ©2022 Silvaco, Inc.

Statistically capacitance values can be positioned in a diagram showing very good results consistency

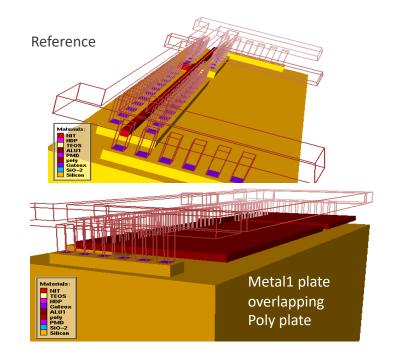

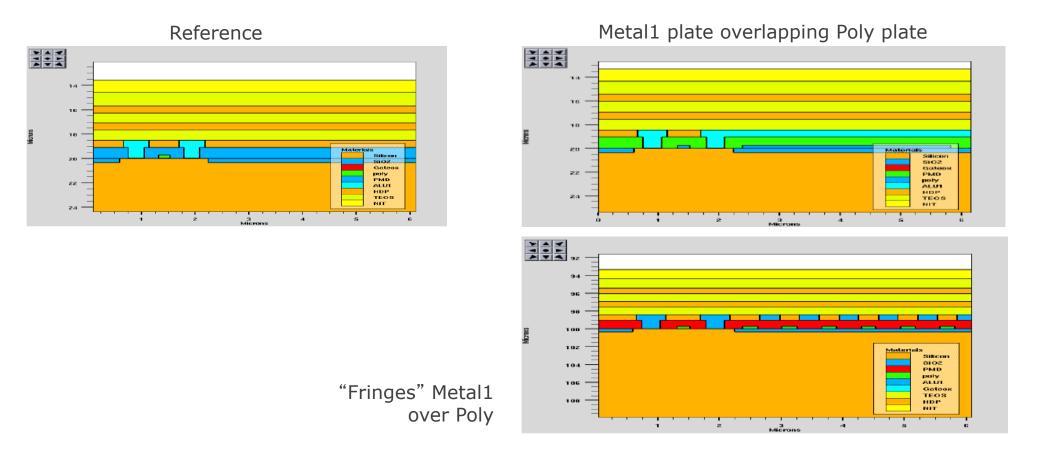

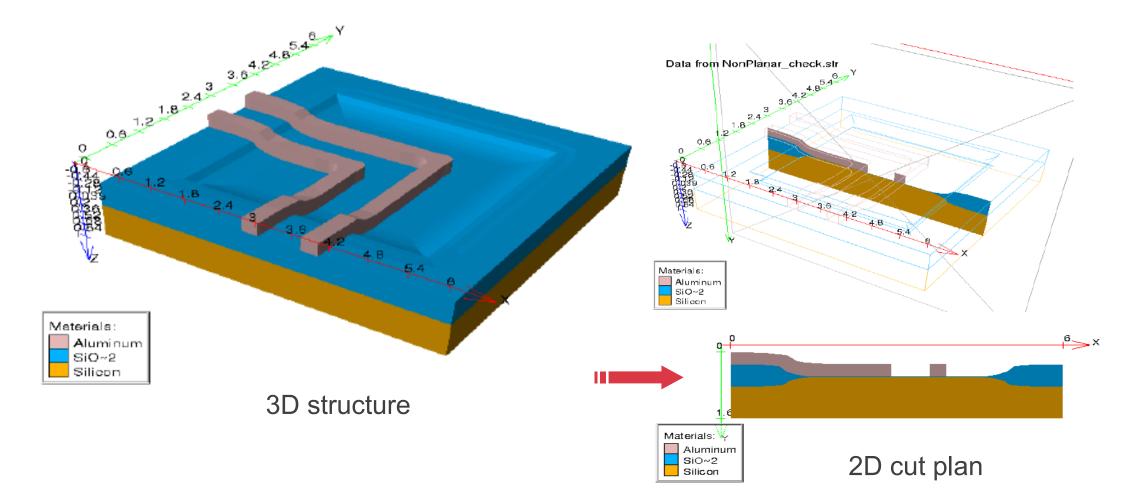

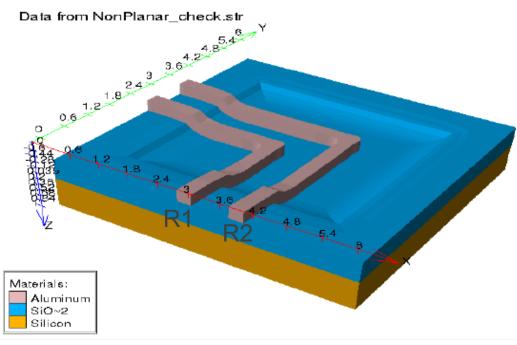

• Three different ring oscillators

• 2D cutplanes of the different ring oscillator

- SPICE simulation results

- Comparison with measurements

|                 | Without     | victoryrcx | diva | mes |

|-----------------|-------------|------------|------|-----|

| Delay ps<br>std | RC<br>39.95 | 48.46      | 43   | 41  |

| Delay ps<br>wcs | 39.95       | 48.39      |      |     |

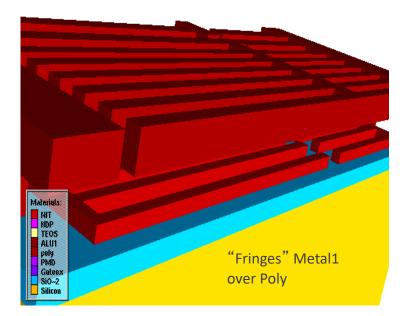

"Fringes" Metal1

over Poly

Reference

#### Metal1 plate overlapping Poly plate

|                 | Without<br>RC | victoryrcx          | diva                | mes       |

|-----------------|---------------|---------------------|---------------------|-----------|

| Delay ps<br>std | 39.95         | 62.98               | 65.4                | 61        |

| Delay ps<br>wcs | 39.95         | 64.21               |                     |           |

|                 |               |                     |                     |           |

|                 | Without<br>RC | victoryrcx          | diva                | mes       |

| Delay ps<br>std |               | victoryrcx<br>59.60 | <i>diva</i><br>79.5 | mes<br>57 |

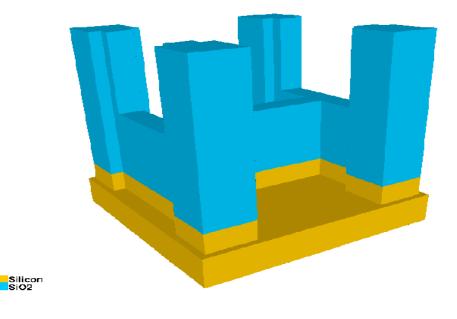

#### **CMOS Sensor**

#### G Sensor

#### CCD Sensor Cell

Comparator 1

#### Comparator 2

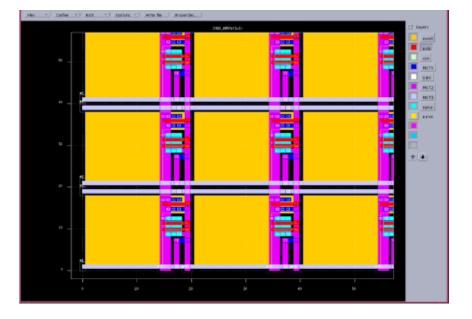

Simulation area (3x3 matrix) posin2 - Abeauan pesin 40 \_ 35 30 25 20 15 ide in 4 10 5 o js sout1 sout2 sout3 S out4 St 10 15 20 25 30 35 0 5 40

#### **SILVACO**

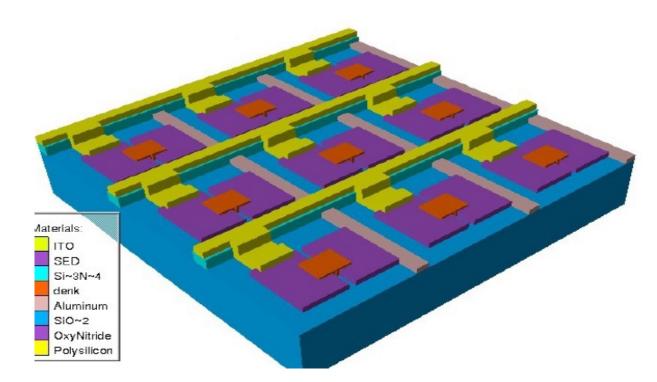

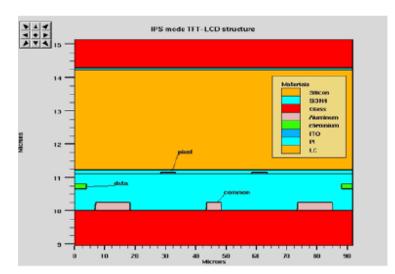

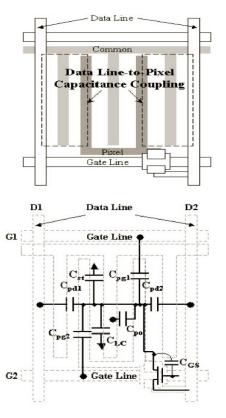

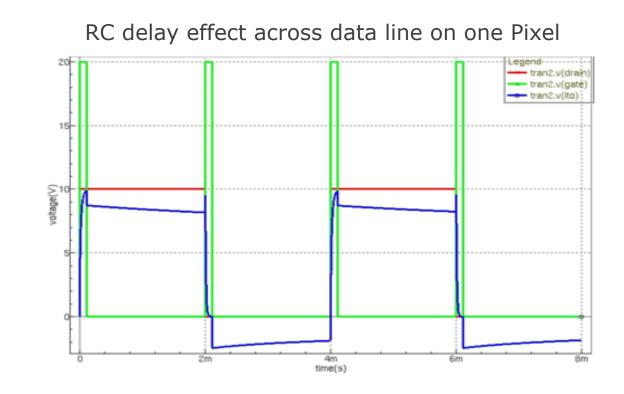

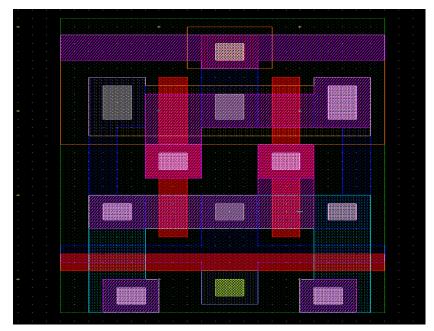

#### Flat Panel LCD, TFT

#### AMLCD-TFT BMT:

|         | Clc<br>(Victory RCx Pro) | Cdc<br>(Victory RCx Pro) | Clc+Cdc<br>(Victory RCx Pro) | Clc+Cdc<br>(Victory RCx Pro) |

|---------|--------------------------|--------------------------|------------------------------|------------------------------|

| pixel_0 | 42.2                     | 61.0                     | 103.2                        | 99.60                        |

| pixel_1 | 32.8                     | 61.1                     | 93.9                         | 93.46                        |

| pixel_2 | 31.6                     | 58.8                     | 90.4                         | 91.25                        |

#### AMLCD-TFT BMT:

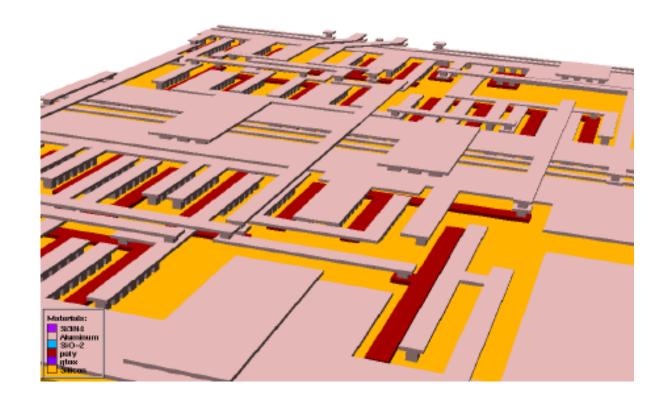

# Memory Cells

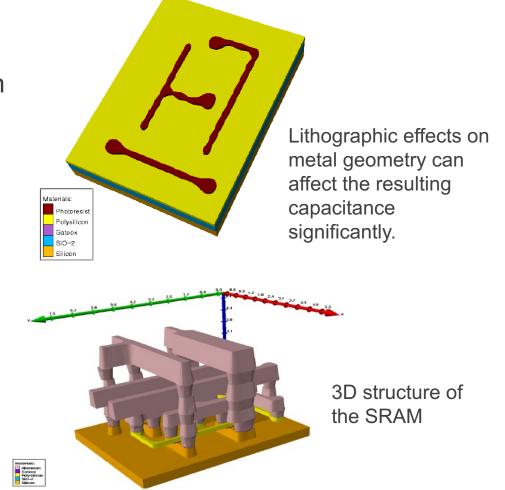

#### SRAM CELL

#### Flash Memory: NOR

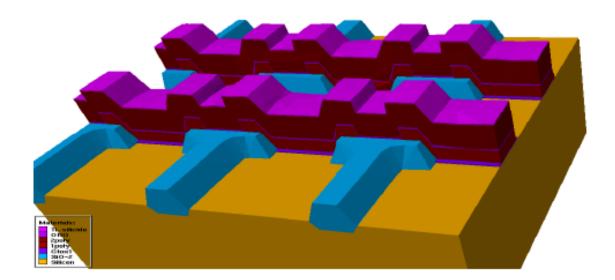

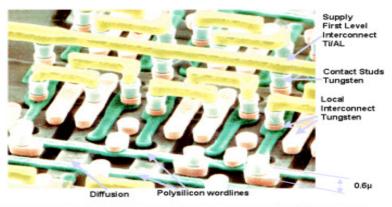

- SRAM and Flash memory cell

- Victory RCx uses advanced 3D process simulation to convert SRAM layout into an accurate 3D representation of the SRAM cell

- Electrical field solutions on the realistic 3D geometry allow accurate extraction of parasitics

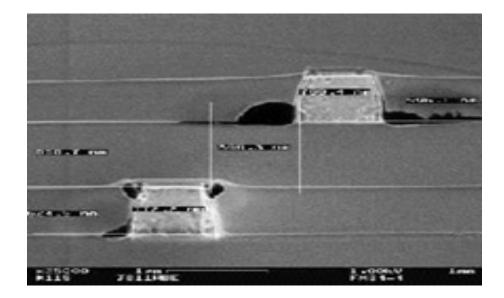

Six memory cells of partially completed SRAM array after removal of oxide insulation. SEM photograph (IBM)

- SEM photography of 2D sectional area

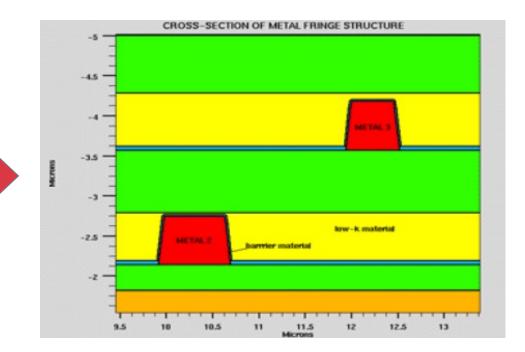

- Cross-section of metal fringe structure

#### **SILVACO**

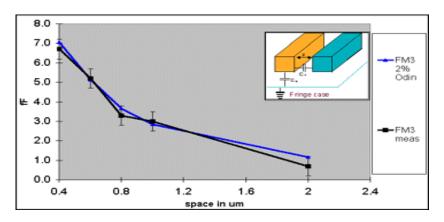

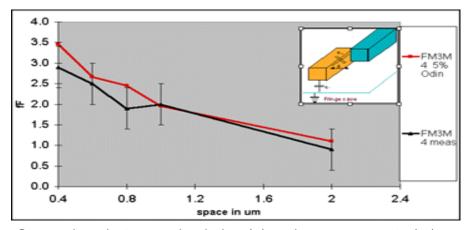

Comparison between simulation (▲) and measurements (■) for lateral capacitance. Two parallel lines of metal 3 of 0.6um width and 100 um length.

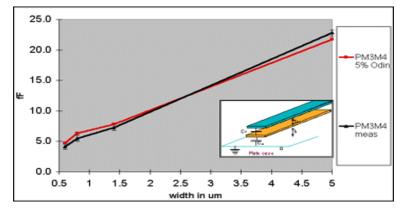

Comparison between simulation (■) and measurements (▲) or different layer fringe or edge capacitance. Two parallel lines of 0.6um width and 100 um length with one line in metal 3 and the other of metal 4.

Comparison between simulation (•) and measurements (•) for two stacked lines. Two parallel lines of metal 3 and metal 4 without any overhang.

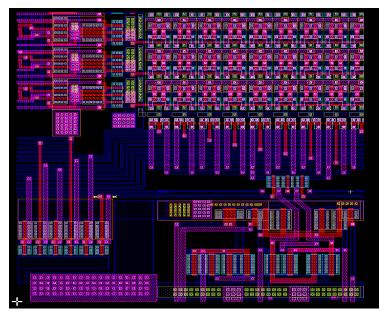

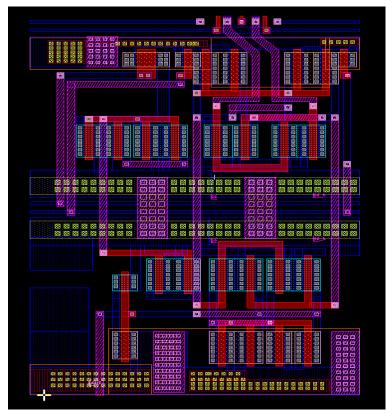

#### SRAM CELL and Decoder, Sense AMP

#### Sense AMP

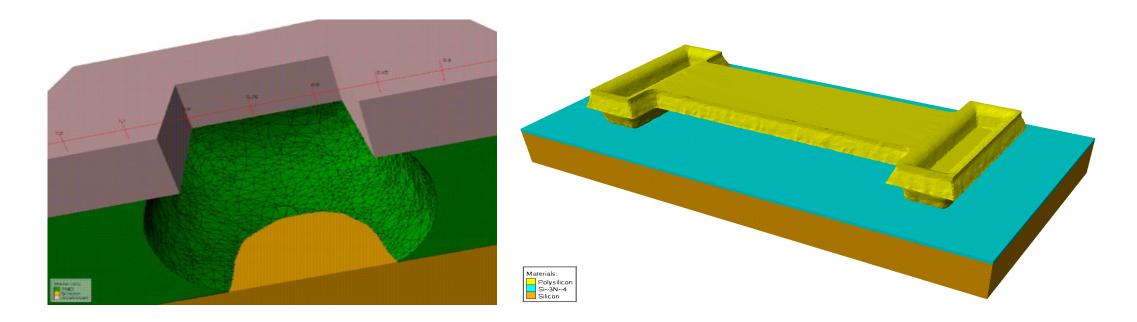

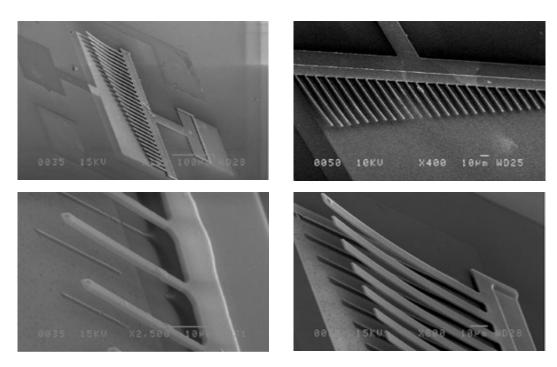

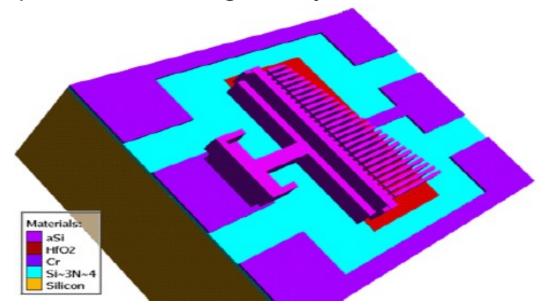

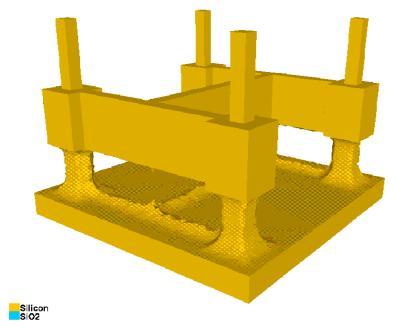

# **MEMS** Simulation

SEM morphologies of the fabricated capacitors with different width and lengths

Results from 3D simulation of the MEMS process flow using Victory RCx Pro

# **MEMS** Simulation

#### A partial creation of an electrostatic MEMS

Part of a MEMS actuator array.

MEMS device after isotropic release etch.

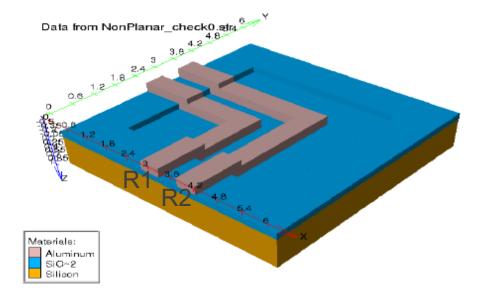

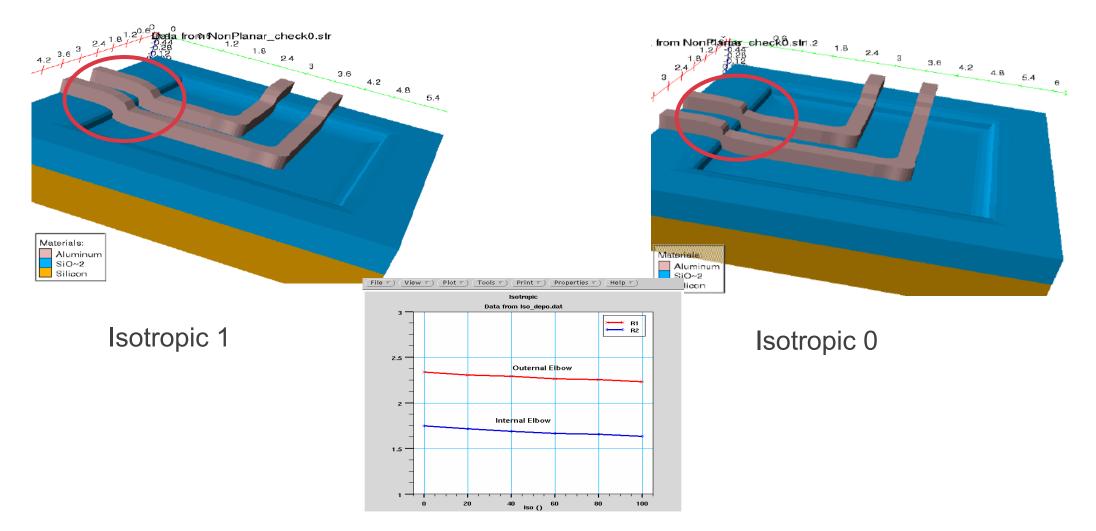

Victory RCx Pro Non-planar pattern:

**TEST** Pattern

| Default Materials Parameter |                       |                       |

|-----------------------------|-----------------------|-----------------------|

| Material Name               | Relative Permittivity | Conductivity [A/V cm] |

| Aluminum                    |                       | 376676                |

| BPSG                        | 3.9                   |                       |

| BSG                         | 3.9                   |                       |

| Copper                      |                       | 588235                |

| Material("string")          | 3.9                   |                       |

| Oxide                       | 3.9                   |                       |

| OxyNitride                  | 7.5                   |                       |

| Nitride                     | 7.5                   |                       |

| Resist                      | 3.9                   |                       |

| Polysilicon                 |                       | 376676                |

| Silicon                     | 3.9                   |                       |

| TEOS                        | 3.9                   |                       |

| Tungsten                    |                       | 200000                |

LOCOS+Litho Physical Process

|    | Physical  | Geometrical |

|----|-----------|-------------|

| R1 | 1.6319044 | 0.9288782   |

| R2 | 2.2651981 | 1.2825422   |

Step Etch + no Litho Geometrical

SILVACO

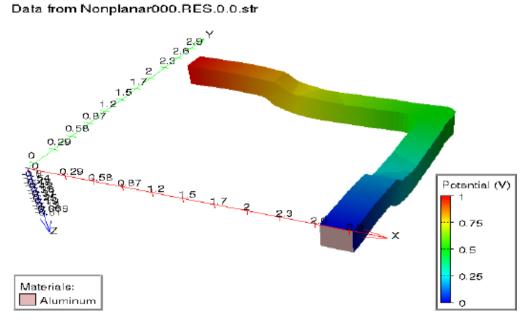

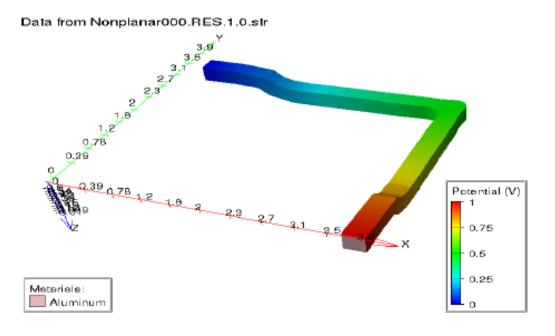

#### Internal elbow electric field

#### External elbow electric field

R=2.2651981

R=1.6319044

# Conclusions

- Victory RCx should be used for parasitic RC extraction where MAXIMUM ACCURACY is required (no simplifications)

- Highly versatile tool ideal solution for

- Via capacitance analysis on 45nm technologies and below (via capacitance is now a significant source of capacitive delay)

- Low Voltage High Speed parasitic analysis for deep sub-micron (Parasitics now dominate delays and signal noise)

- True 3D process effects are important for accurate SPICE results

- TFT pixel arrays where many conformal depositions make capacitance analysis using traditional rule based tools too inaccurate due to multiple topology effects